3D集成新方案,实现千倍芯片性能提升!

文章导读: 随着摩尔定律逐步进入平台期,目前半导体芯片的性能提升已经越来越多地依赖芯片架构设计以及高级封装技术的提升,而不是依靠半导体工艺体征尺寸的下降。另一方面,随着人工智能时代的来临,越来越多的计算芯片设计需要考虑人工智能对于算力的需求.

随着摩尔定律逐步进入平台期,目前半导体芯片的性能提升已经越来越多地依赖芯片架构设计以及高级封装技术的提升,而不是依靠半导体工艺体征尺寸的下降。另一方面,随着人工智能时代的来临,越来越多的计算芯片设计需要考虑人工智能对于算力的需求。因此,如何在未来十年内为人工智能应用来设计和优化相关的芯片架构、工艺以及封装系统就成了学术界和工业界都非常关注的问题。

在上周召开的2021国际电子器件大会(IEDM 2021)中,我们就看到了许多相关的研究发表,而其中非常值得我们关注的就是一篇来自MIT和斯坦福大学的论文,标题为《The Future of Hardware Technologies for Computing: N3XT 3D MOSAIC, Illusion Scaleup, Co-Design》(《面向计算的未来硬件平台:N3XT 3D MOSAIC与Illusion Scaleup协同设计》)。该研究并非是一日之功,而是以MIT和斯坦福大学为代表的美国半导体工艺学术研究学派在超高密度3D集成领域多年研究的最新成果,并且还规划了未来的路线图。

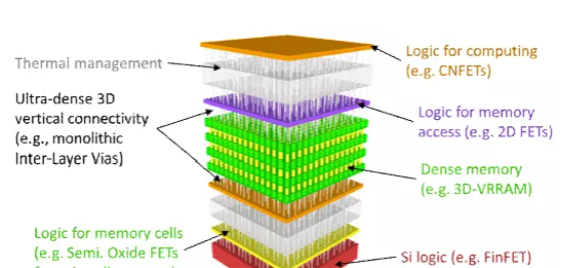

目前,虽然以TSV为代表的3D集成技术已经成熟,但是3D集成的通孔之间的间距仍然较大,在10um数量级。为了能进一步提升3D集成密度,美国半导体学术界(以斯坦福的黄汉森,Subhasish Mitra和MIT的Max Shulaker为代表)提出的方案是使用碳纳米管技术。碳纳米管技术的一个重要优势就是可以实现超高密度3D堆叠通孔,其通孔间距可缩小至100 nm,比目前的TSV通孔间距缩小了两个数量级。同时,考虑目前人工智能应用,其主要的性能瓶颈在于内存访问,因为人工智能所需要的神经网络模型运行时无论是权重还是中间结果都需要大量的内存资源,因此需要把存储器和计算逻辑以非常高的效率集成在一起。两者相结合,就是使用碳纳米管技术和超高密度3D集成技术把计算和(新)存储器集成在一起,而美国半导体学界提出的解决方案就是N3XT,全称是“基于纳米工程的计算系统技术”。具体来说,N3XT把多种使用不同工艺实现的芯片层(包括用传统硅工艺实现的数字逻辑,使用下一代存储器工艺实现的高密度存储器,使用碳纳米管工艺实现的计算逻辑等)使用超高密度3D集成通孔集成到了一起。

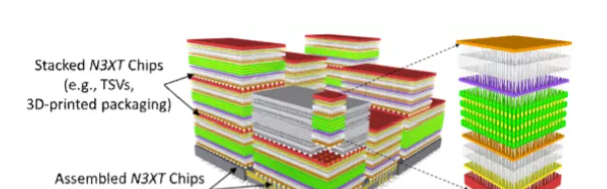

以N3XT为单元,还可以把多个不同的N3XT单元(以及传统的芯片)以各种形式进一步集成到一起,例如可以用TSV的形式把多个N3XT单元堆叠在一起,也可以用2.5D封装的形式把多个N3XT封装到通过一个硅基板上,由此实现超大规模的异构集成。这种把多种芯片以各种方式集成到一起的方案称之为MOSAIC(即Monolithc/stacked/assembled IC,指以各种不同形式集成到一起的芯片单元)。

至此,该研究中的主要工艺和器件技术(即论文标题中的N3XT 3D MOSAIC)已经呈现在了我们眼前。下一步就是如何在系统层面上最大化这种规模化集成的效率。

超高密度3D集成配合系统优化实现千倍性能提升

随着人工智能对算力的需求越来越高,未来的N3XT系统也需要考虑在系统层面上如何最优化以满足人工智能的算力需求;换句话说,如果给100个N3XT系统,如何最优化地分配任务,让整体计算效率最高?这个问题如果能解决地好,就能很好地处理N3XT系统对于人工智能计算问题的规模化(scale-up)。

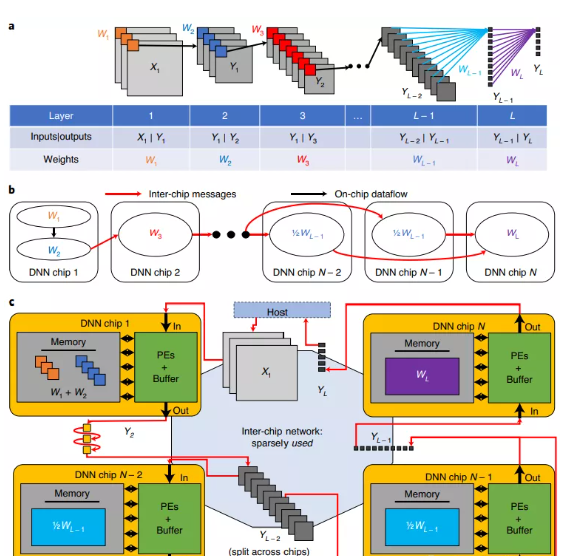

对此,研究者提出的方案是Illusion Scaleup。Illusion scaleup主要是针对人工智能应用中的深度学习算法。该系统设计方法中,首先把整个神经网络分割成多个部分,并且给每个N3XT模块分配一部分计算任务。例如,分割可以以神经网络层为单位,当一层的计算量比较小的时候,可以在单个N3XT模块上分配多个层的计算;当一层的计算量较大时,则可以把一层网络也分割成多个部分给不同的N3XT模块。由于神经网络不同的层之间是串行计算关系,因此通过这种以层为单位来分割工作量,就可以让不同的N3XT模块之间以流水线的方式工作。另外,由于每个N3XT只负责一层计算,因此可以确保神经网络的权重不用在模块间移动,而仅仅只需要移动中间结果,这样就大大减小了数据移动带来的额外开销。

最后,由于N3XT系统可以使用下一代非易失性存储器,例如RRAM,因此可以支持快速开关,针对于此作者还提出了可以利用此特性在不需要使用某个N3XT单元的时候把它关闭,从而可以大大节省漏电流。使用这样的策略,可以通过线性增加每个N3XT的性能(例如增加N3XT堆叠层数,以及N3XT之间的互联带宽)来满足人工智能计算对于算力指数级上升的算力。使用这样的方法,研究表明整个N3XT 3D MOSAIC可以实现比目前3D堆叠100-1000倍的性能提升。

超高密度3D集成商用化的道路

目前美国半导体学术界对于碳纳米管和N3XT相关技术的商用化决心很大,目前也有不错的成果。整体来说,碳纳米管在美国的商业化过程中包括了多方的加入:美国政府研究机构DARPA,高校MIT和斯坦福,以及美国专门负责先进半导体技术代工的代工厂SkyWater。DARPA从多年前就开始大力资助碳纳米管相关的下一代半导体工艺研究,两年前,MIT的Max Shulake已经带领研究组在SkyWater实现了首个碳纳米管和RRAM的3D堆叠芯片晶圆,而在最近的两年中,同样的团队陆续完成了多个里程碑,包括首个碳纳米管实现的超大规模集成电路(RISC-V处理器),首个碳纳米管PDK等等。同时,在整个碳纳米管研究团队中起领袖作用的斯坦福大学教授黄汉森本人曾于2018-2020年学术休假期间全职担任TSMC的副总裁,而在回到斯坦福大学之后仍然担任TSMC的首席科学家职位,相信他也会成为碳纳米管超高密度3D堆叠技术商用化的重要桥梁人物。

而在另一方面,在半导体工业界,对于大规模高密度3D封装的追求也是历历可见。例如,AMD今年早些时候发布的3D V-Cache使用了TSMC的最新SoIC技术,可以将3D堆叠通孔间距下降到1um数量级,从而大大增加了3D堆叠的互联密度。Intel也同样在今年发布了Ponte Vecchio,可谓是它最雄心勃勃的芯片计划,借助TSV以及Intel特有的EMIB技术实现了超大规模2.5D和3D互联以及封装。半导体业界对于下一代超高密度封装和互联非常强的诉求以满足人工智能高性能计算的需求,在这样的情况下,我们认为N3XT 3D MOSAIC从学术界的角度给出了一个未来相关技术的进化路线图,其中至少有一部分(例如3D MOSAIC)会在未来几年内落地到商用中,而碳纳米管技术随着更多研究和验证,也可望在稍远的时间节点正式进入商用。

在中国,相关的碳纳米管技术在学术界也有很好的研究积累,北大的彭练矛院士等团队也在全球顶级期刊上发表了非常具有影响力的研究结果。超大规模高密度3D集成是一项系统工程,需要半导体工艺和器件,先进封装技术以及电路架构领域的协同发展,我们希望中国的相关技术能从目前的碳纳米管器件的单点突破真正拓展到系统级突破,同时配合半导体代工和封装业界的发展,这样才能在下一代基于新一代器件和封装技术的半导体新范式来临时,能有足够多的技术积累来引领整个技术潮流的发展。

本资讯来源于半导体行业观察,仅限于分享,交流,如侵权请联系管理员进行删除!

赢咖7清洗机12年专注研制等离子清洗机,等离子体清洗机,等离子清洗设备,常压大气和低压真空型低温等离子表面处理设备,大气低温等离子体表面处理系统,大气常压收放卷等离子表面 设备处理的国家高新技术企业,赢咖7严格执行ISO9001质量体系管理,生产的等离子清洗机通过欧盟CE认证,为电子、半导体封装、汽车、yi疗等领域的客户提供清洗、活化、刻蚀、涂覆的等离 子表面处理解决方案,是行业内值得信赖的等离子清洗机厂家。如果您想要了解关于产品的详细内容或在设备使用中存在疑问,欢迎点击赢咖7的在线客服进行咨询,或者直接拨打全国统一 服务热线400-816-9009,赢咖7随时恭候您的来电!赢咖7推荐

行业资讯

- 医疗导管等离子蚀刻机介绍

- 赢咖7注册通过高新技术企业重新认定

- 我国新能源汽车销量蝉联全球第一,新能源汽车促进等离子清洗机表面处理事业发展!

- 苹果发布两颗芯片:M2 Pro 和 M2 Max,等离子清洗机能够应用在上面吗?

- 2022年硬盘出货量:大幅下跌,接近腰斩,这对等离子清洗机有什么样影响呢?

- 博世在苏州投资建立新能源汽车核心部件及自动驾驶研发制造基地,促进等离子清洗机行业发展!

- 2022年汽车销量2686.4万,新能源市场占有率达到25.6%,等离子清洗机的能够带来什么变化?

- 确保芯片供应充分,重塑汽车产业集群,等离子清洗机成为汽车领域的一员呢?

- 电子后视镜正式在我国获批,新的市场出现,等离子清洗机能够做哪些工作呢?

- 中国半导体销售,同比大跌21.2%,等离子清洗机如何发展半导体方面的表面处理工艺?